pg电子官网功率半导体器件学习笔记(1)理论白痴的我写这个压力有点小大,水平很有限,初学者看看,然后再去找对应论文看正规的说法和解释,别被我误导,老司机跳过。

功率半导体器件,以前也被称为电力电子器件,简单来说,就是进行功率处理的,具有处理高电压,大电流能力的半导体器件。典型的功率处理,包括变频、变压、变流、功率管理等等。早期的功率半导体器件:大功率二极管晶闸管等等,主要用于工业电力系统(正因如此,早期才被称为电力电子器件)后来,随着以功率MOSFET器件为代表的新型功率半导体器件的迅速发展,现在功率半导体器件已经非常广泛,在计算机、通行、消费电子汽车电子为代表的4C行业(computer、communication、consumer electronics、cartronics)。在大多数情况下,它是被作为开关使用(switch),开关,简单的说,就是用来控制电流的通过和截断。那么,一个理想的开关,应该具有两个基本的特性:电流通过的时候,这个理想开关两端的电压降是零;电流截断的时候,这个理想开关两端可以承受的电压可以是任意大小,也就是0~无穷大。

因此,功率半导体器件的研究和发展,就是围绕着这个目标不断前进的。现在的功率半导体器件,已经具有很好的性能了,在要求的电压电流处理范围内,可以接近一个比较理想的开关。举几个例子,功率二极管,晶闸管,还有功率BJT(就是功率双极型晶体管)这些都是第一代产品了,比较老的了,第二代是以功率MOSFET为代表的新型功率半导体器件,如VDMOS、LDMOS,以及IGBT。VDMOS 即(vertical double-diffusion MOSFET)是纵向器件,栅和源电极在上面,漏极在下面,多用于分立器件;LDMOS 即(Lateraldouble-diffusion MOSFET),是横向器件,其三个电极(源极栅极漏极)均在硅片上表面,易于集成,多用于功率集成电路领域。IGBT 即(InsulatedGate Bipolar Transistor绝缘栅双极型晶体管),可以看作是功率MOS和功率BJT的混合型新器件。(这一段是摘抄与修改)

在源端加P+,引出电极和源级短接,保持源和衬底电位一致,消除衬偏效应对阈值电压Vth的影响。直接让P-body和源级相连理论上也行,但轻掺杂的P-body接触电阻更大,所以采用源区加P+的方法来降低接触电阻。这这只是解决方法之一,不是唯一。

个人觉得MOS是个很重要的概念,知道一些基本原理才能进行学术研究,所以MOS的特性一定要掌握到位。

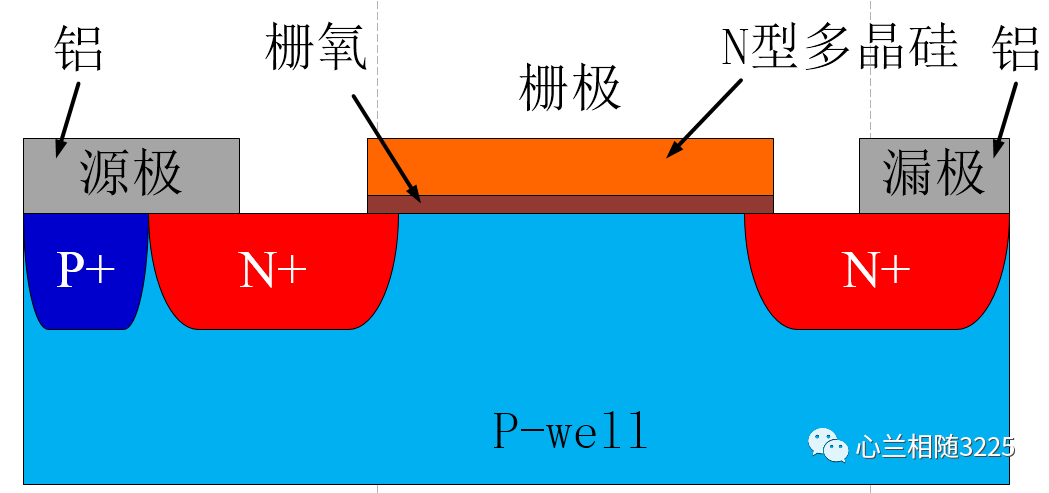

下图是一个典型的NMOS示意图,源极下方P+是为了消除衬偏效应的影响,同时也为了降低接触电阻。栅氧一般很薄很薄,而且栅氧要求的质量很高,氧化层的形成一般有干氧氧化和湿氧氧化,栅氧一般(不是所有)采用干氧氧化,干氧虽然慢,但质量高。栅氧上面是多晶硅,多晶硅还需要掺入五价的元素(如磷,砷)形成N型多晶硅。为什么不掺硼这样的元素形成P型多晶硅,一种说法是栅氧(SiO2)具有吸硼排磷的特性,假如多晶硅里有硼元素,那么就可能会进入栅氧,栅氧里便会掺入杂质,影响栅氧质量,甚至会出现我们极其不希望看到的栅电流。对了,个人觉得,在流片的时候,记得将靠近场氧等氧化层的P-区增大一下表面浓度哦,不然吸硼排磷,发现P-body最上面竟然不是P-,而是漂移区,硼都被氧化层吸走了,这就哭了,流片成本那么高,emmm毕竟流片良率问题太重要了。

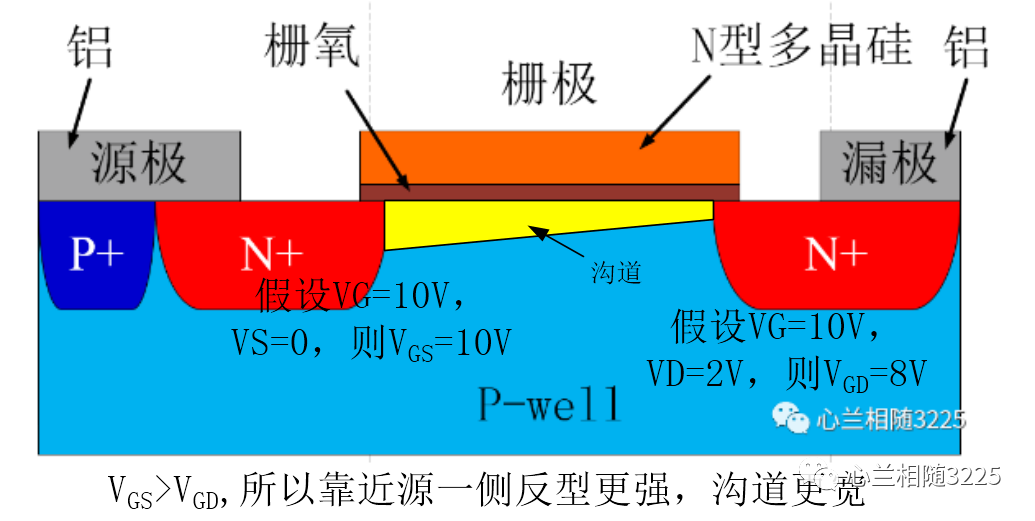

高压排斥空穴,低压吸引电子这是大家都认同的。栅极加高压,靠近栅氧的P-well区空穴便会被排斥开,留下不可移动的硼离子,这些阴离子形成的便是反型层,对于电子来说是低阻区,这就是所谓的沟道,而且,栅压越大沟道越宽沟道电阻就越小。

当栅氧较厚时,pwell浓度较大时,反型较困难,即需要更大的栅压才能形成反型层,也就是阈值电压会增大,而且阈值电压也跟温度有关系哦,温度升高,阈值电压是降低的,因为Vth的表达式中有一项是与表面势有关的,而表面势与温度的是正比关系,即温度升高表面势增大。在阈值电压的表达式中,Vth=Vth0+γ((Φ-Vbs)^0.5-Φ^0.5),显然第二项是负值,也就是说表面势Φ增大Vth减小。

当沟道形成,漏极电压不大时,这个时候MOS的导通基本是受沟道电阻的影响,所以呈现的是线性区变化,

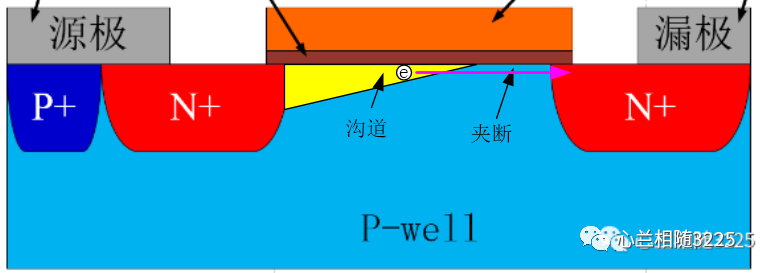

随着漏压继续增加,靠近漏的沟道消失,形成夹断,一方面,不是所有的电子都可以通过夹断区,只有速度高的电子才能在电场作用下强行穿过夹断区,另一方面,电子也是有饱和速度的,速度达到一定值不再增加,这就是为什么漏压增加了,电流却饱和不增加的原因。在功率器件,比如VDMOS中,饱和区的电流曲线不是平的,而是上翘的,是因为两个P-body之间N-drift区即JFET区,更多的漏电势落在了JFET电阻上,所以在沟道夹断以后还是会电流上翘的现象,也就是准饱和效应。准饱和效应我涉猎较少,对此感兴趣的多去查查文献哦。

击穿分为硬击穿和软击穿,如果BV曲线突然上升,很陡,就称为硬击穿,如果BV曲线上升很缓,称为软击穿。

IGBT正常导通应该是栅下沟道开启,电子从发射极出发,经过沟道,进入漂移区,到达并聚集在集电极下方,当集电极与集电极下方电位大于PN结的正向导通压降,集电极P+和N-buffer构成的PN结就会开启,器件不再只有电子电流,而且有空穴电流,进入双极型模式,发生电导调制,即大注入(少子数量大于等于多子数量),电流能力大大增强。当栅压降低pg电子网址,让沟道下方电子反型层消失,电子电流就会被切断,IGBT关断。

但是当漂移区的空穴经源区P-bodypg电子网址、源区P+流到源极时,由于P-body区电阻的存在,在源区P-body和源区N+可能产生一定的压降,当该压降大于由源区P-body和源区N+组成的PN结的正向导通压降时,由源区N+、源区P-body和N-drift构成的寄生NPN就会开启,此时栅对于沟道电流就失去了控制,无法通过栅压让器件关断,这就是闩锁效应,一般发生在IGBT内,示意图如下。(我自己口述解释的,很不严谨,意思大概懂即可)

工艺上为防正向导通期间寄生NPN开启的方法是增大P-body的浓度,我们知道,掺杂越多,载流子就越多,电阻就越小,P-body电阻小,那么较大电流流过时,就很难在发射极N+和P-body之间形成0.7伏的正向导通压降,发射极P-body/N+结就较难开启,可以达到防闩锁的目的,但是这样会导致阈值电压的增大。

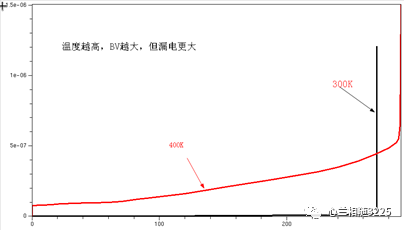

温度升高,晶格振动剧烈,载流子迁移率因受阻而下降,故相同电压下,温度高的,速率更低,需要更大的电压才能使得载流子达到雪崩击穿的速率,因此温度升高,击穿电压是变大的,但是温度升高,本征激发的载流子数目也在变多,所以漏电也会增加,仿真结果如下。

对于PN+结来说,空穴是更少的少子,对于P+N结,电子是更少的少子,空穴迁移率小于电子,所以要想达到雪崩速率,PN+需要更大的电压,PN+的BV高些,仿线、SOI技术的优缺点

对于一般的IGBT,如上面第5条的图所示, IGBT不存在体二极管,当器件关断的时候,漂移区空穴可以通过发射极P+抽取,但是电子就惨了,没有路径让它回家,集电极的P+对于电子而言是高阻区,于是电子就只能被漂移区内的空穴慢慢复合掉。复合的速度哪能比得上抽取的快,所以IGBT最严重的问题就是关断速度贼鸡儿慢,这就导致了IGBT只能用于大功率,可惜在高频领域无用武之地。

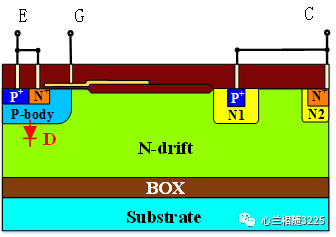

为了解决这一头疼问题,必须要让IGBT关断期间长长的拖尾电流消失,怎么办呢?最简单的就是也给电子一条回家的路径,那就是在集电极侧加一个N+区同时与集电极连接起来,这样电子的抽取就变快了。IGBT发射极(E)也被叫阴极,集电极(C)也被叫阳极。

子抽取路径,加快IGBT关断的。正常的IGBT是左边低压右边高压,电流从右向左。但是加了阳极N+之后,左边可以接高压,右边可以接低压,体二极管可以导通,电流从左向右,实现了逆向导通的功能,所以叫逆导,reverse conduction,这是RC的来历。由于阳极P/N1结被短路,RC-IGBT 正向导通初期(发生电压折回之前)体内只有电子电流,阳极P+区不能向漂移区注入空穴,漂移区因此也没有电导调制效应存在。也就是说,RC-IGBT发生电压折回之前的导通电阻实际非常大,其值接近于相同结构尺寸下VDMOS的导通电阻。当阳极P+和N1下方电位大于阳极P/N1结的内建电势时,阳极P+开始向漂移区注入空穴,使漂移区发生电导调制效应,降低漂移区的电阻。这会导致 RC-IGBT 的电流增大,使 N1下方的电势进一步下降,结果会使漂移区有更多的空穴注入和更充分电导调制效应,这样就会形成电流不断增大而电阻不断减小的正反馈过程。这个过程反映到输出特性曲线的结果,即为 RC-IGBT 的电流增大同时电压减小的电压折回现象。

简单来讲就是MOS小电流模式切换到BJT大电流模式需要经历突变这个过程。snapback现象的存在是不希望看到的,因为一个电压对应值两个电流,如果两个玩意并联,电压是相同的,可能会存在一个流过电流大一个流过电流小,流过电流大的阻碍就变小,就会导致电流越来越大,可能会引起器件损坏。工程上一般是增大阳极N+和P+之间的距离,这样可以利用N+和P+之间漂移区电阻来形成压降,让N1下方电势早点比阳极电位小0.7V(假设PN结开启电压是0.7V),但这样又太费面积,学术上的研究一般是通过让电子绕路增大上述电阻,这方面论文太多了,感兴趣去研究研究呢。

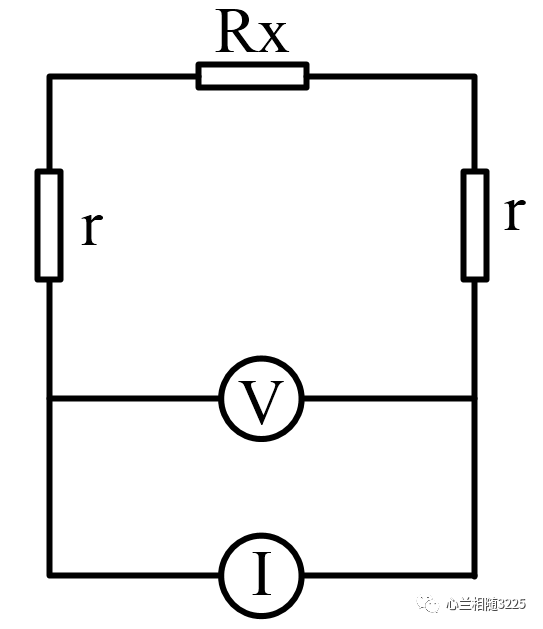

采用四线法测量时,由于四条引线分别形成电压回路和电流回路,电压测量回路的阻抗很大,流过的电流可以忽略,Rx=U/I是更加精确的,所以四线法测电阻被广泛采用。

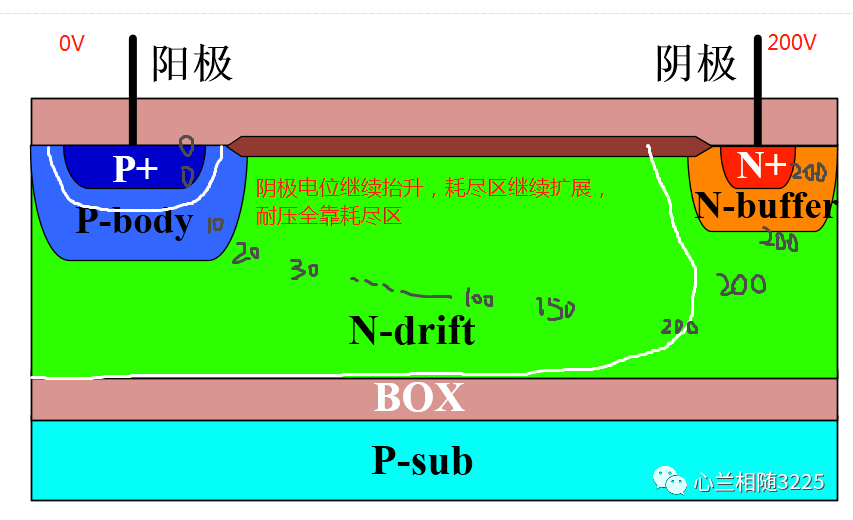

其中:EBR为临界击穿电场强度,ε0为自由空间介电常数, εr为相对介电常数,ND为施主浓度。根据上式,我们可以看出,要想使二极管具有较高的击穿电压 VBR,硅片初始材料应具有较低的施主杂质浓度 ND,也就是说要具有较高的电阻率。为了能够让空间电荷区在反偏时有足够的扩展空间,FRD 的漂移区还必须具有比较大的厚度。但对于低正向压降的要求来说,必须保证载流子具有较长的寿命以保证在正向大注时实现高度的电导调制。因此高反向击穿电压和低正向压降对高阻层的要求是相互矛盾的,在器件设计时要考虑到。下面我只是想把耗尽过程表达清楚,耗尽线是我随便瞎画的。个人认为PN结的耐压过程很重要,初学者一定要去查阅

图中黑色的数字,代表各位置的大致电位,这里想表达的是,电势只会在耗尽区进行降落,耗尽区以外的区域电势不变,称为中性区,换句话说,只有耗尽层的展宽程度才是耐压大小的决定性因素。所以对于高压应用的场合,普遍采用N漂移区来提升器件的耐压特性pg电子网址。

器件提前击穿原因有很多,比如某处电场太强(通常在鸟嘴处,沟槽栅拐角等这些曲率较小的地方),超过硅基的临界击穿电场(一般认为25万-30万V/m)。

理论这种东西基本上全靠自己去悟,没有谁可以指导谁,也不是教授博士说的就一定是对的,论文都有错的,比如很多论文里的NMOS的N说成N-type,但严格来讲是指N-channel,从来没有N-type这种说法。公众号里写的肯定有错误的地方,但我觉得错不可怕,如果看一个公众号可以提起你对这一方向的兴趣,从而好像找到了自己的方向,开始去搜索研究论文,于仿真,测试等等,我想这个公众号就是成功的。

Copyright © 2002-2025 PG电子(中国)官方网站 版权所有 非商用版本HTML地图 XML地图txt地图 备案号:冀ICP备18038649号-1